# Планировщик ПЛИС FPGA System Planner (FSP)

Release SPB\_16.6

Александр Акулин

PCB SOFT

Официальный дистрибутор Cadence Design Systems

[wwwpcbsoft.ru](http://wwwpcbsoft.ru)

**cadence®**

# Введение в FPGA System Planner

# Зачем нужен FPGA System Planner?

1. Существующий процесс проектирования ПЛИС

2. Дизайн ПЛИС с использованием Cadence FSP

3. Маршрут проектирования

4. Приложения

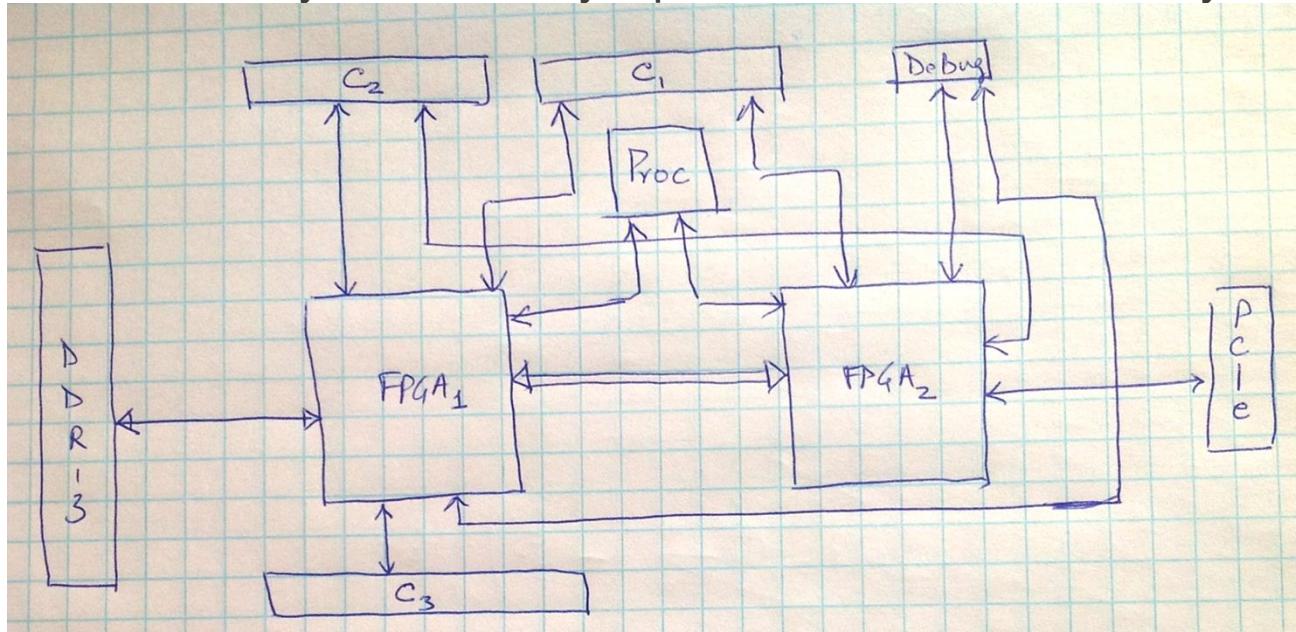

# Как обычно идет проектирование архитектуры и размещения вашей платы?

- На бумаге или в графическом редакторе?

- Как определить расположение компонентов и оптимальное расположение каналов обмена данными?

- Какие сложности возможны с точки зрения проектов ПЛИС?

- Какие проблемы со стороны конструкции печатной платы?

- Этот проект вообще реализуем?

- Мы не будем в этом уверены, не выполнив следующие шаги

# Выбор ПЛИС

- Достаточное ли количество выводов у ПЛИС?

- Достаточно ли ресурсов в ПЛИС?

- Не придет ли к нам в конце проектирования отдел маркетинга с новыми требованиями, которые потребуют изменения выбора ПЛИС?

- Будет ли эта микросхема в этом корпусе доступна в течение времени, необходимого на проектирование и позже, в процессе продаж – или придется в дальнейшем ее заменять?

Обсуждаем, решаем и двигаемся дальше!

# Проектирование ПЛИС и назначение выводов

- Excel и / или средства проектирования FPGA

- Совместная работа дизайнера ПЛИС и схемотехника

- Определение банков ПЛИС, требующих разного питания – надо иметь в виду расположение ПЛИС на печатной плате в процессе назначения выводов!

- Назначить выводы вручную или полуавтоматически

Передаем таблицу выводов схемотехнику в Excel или тексте

# Создание схемы и трассировка платы

- Создаем символы ПЛИС исходя из проекта ПЛИС, или используем библиотечный символ ПЛИС

- Чертим схему, чтобы создать соединения в соответствии с определением выводов ПЛИС

- Упаковываем проект и передаем в редактор печатных плат

- Тут вы впервые видите размещение компонентов и картину связей!

- Как вы теперь делаете изменения в назначении выводов?

- Предлагаете внести изменения разработчику ПЛИС, или трассируете все «как есть»?

# Но что если...

- Проект ПЛИС требует от вас выбрать другой тип ПЛИС?

- Команда механиков и тепловиков требует от вас подвинуть некоторые компоненты на слой Bottom?

- Недоступность ПЛИС в продаже привела к необходимости смены парт намбера ПЛИС?

- У отдела продаж появились новые требования к функционалу прибора?

- Плату с ПЛИС гораздо труднее изменить, чем прошивку ПЛИС

- Изменения платы становятся критическим местом в проекте

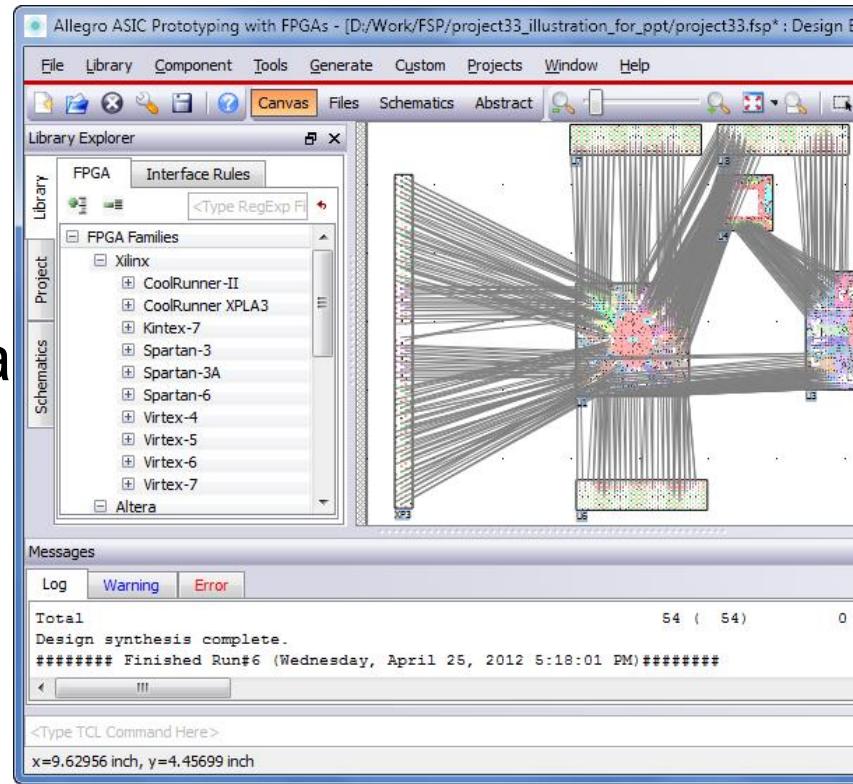

# Проектирование ПЛИС с Allegro FSP

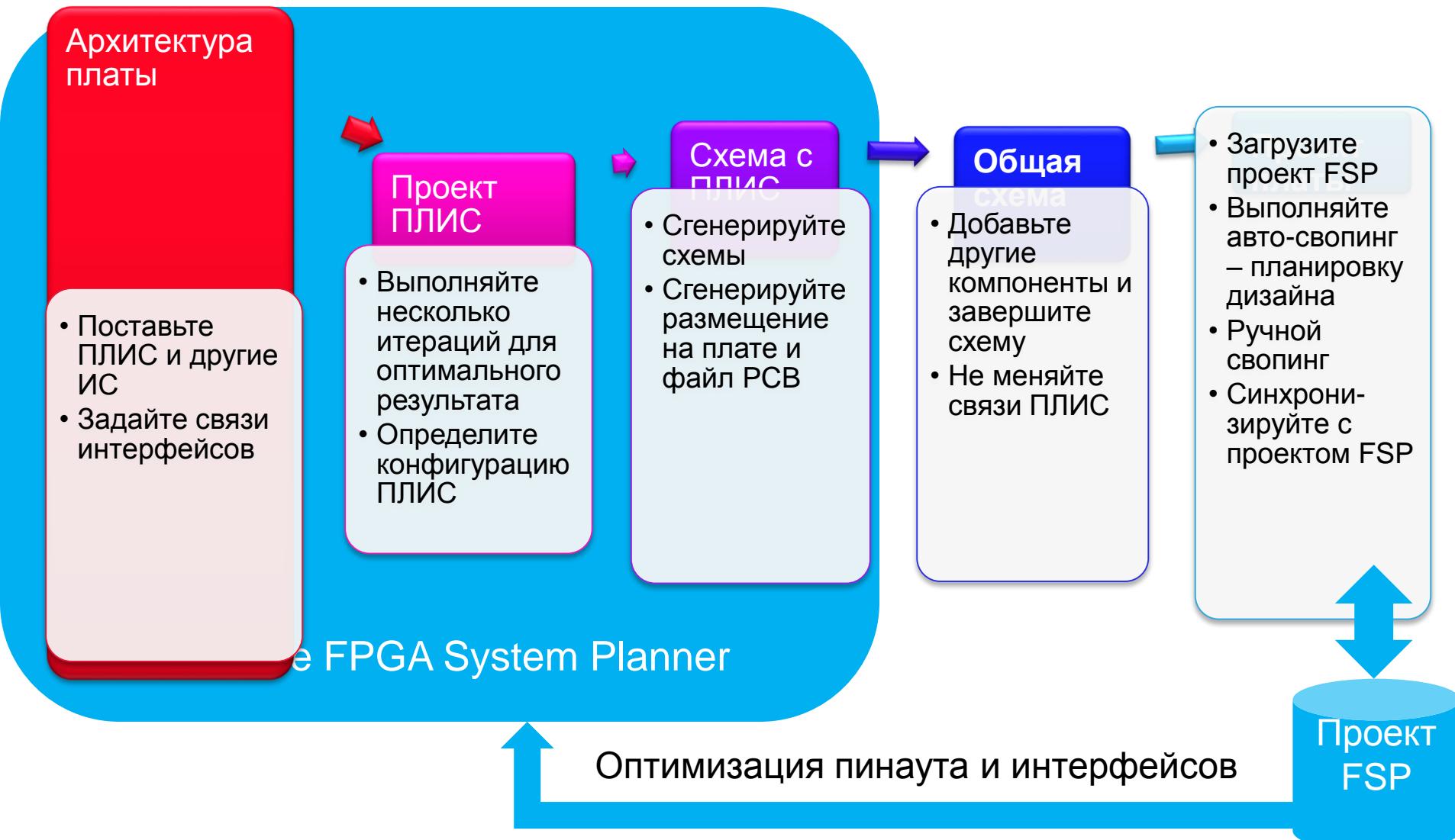

# Архитектура печатной платы

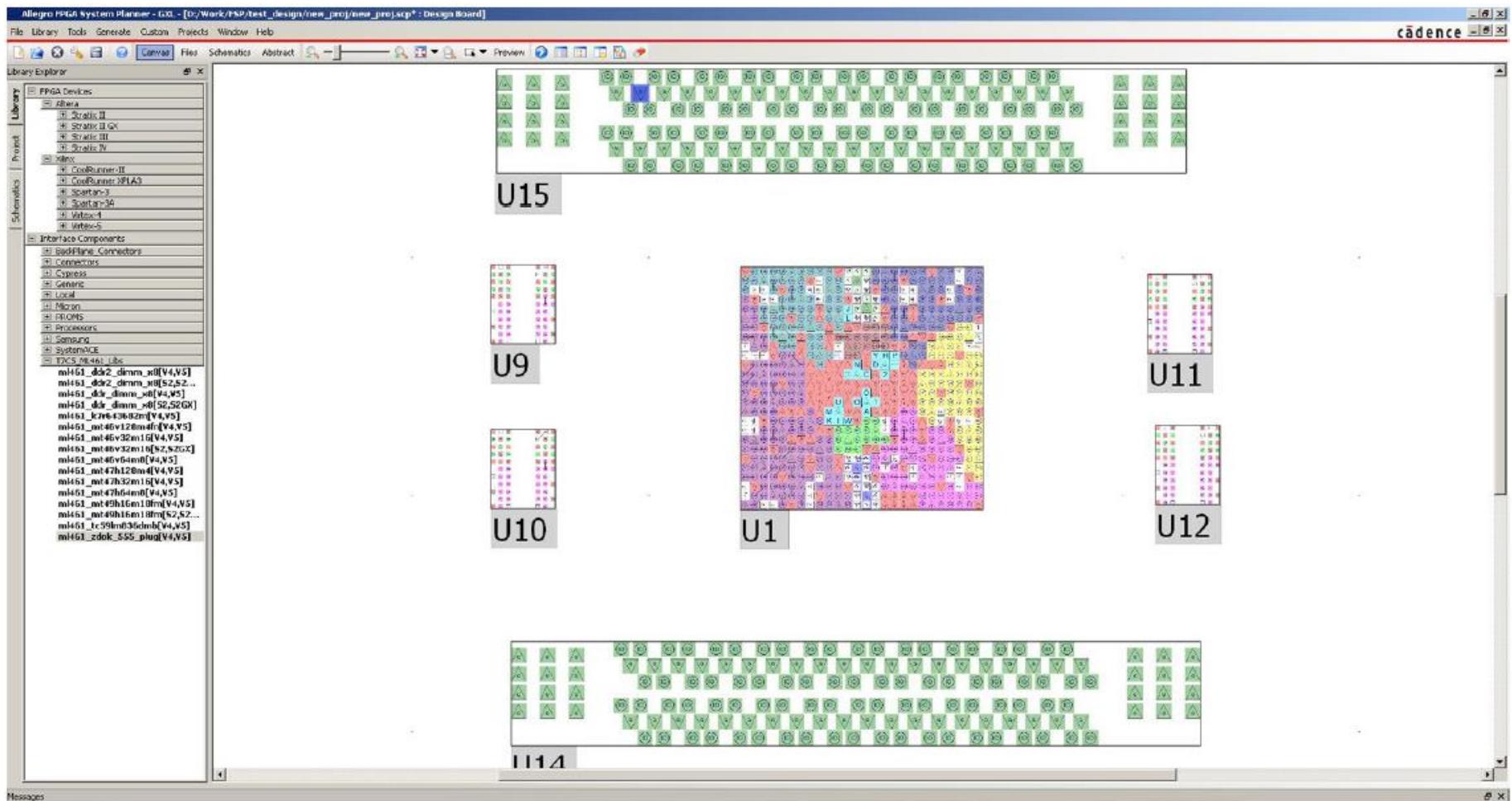

- FSP предлагает редактор, который визуализирует реальную будущую плату

- Поставьте компоненты из вашей библиотеки на листе FSP

- FSP использует патентованную, основанную на правилах, машину для синтеза выводов I/O, автоматически определяя оптимальные связи

- С этими ключевыми возможностями, вы можете пробовать разные архитектуры перед тем, как смотреть на реальное размещение платы

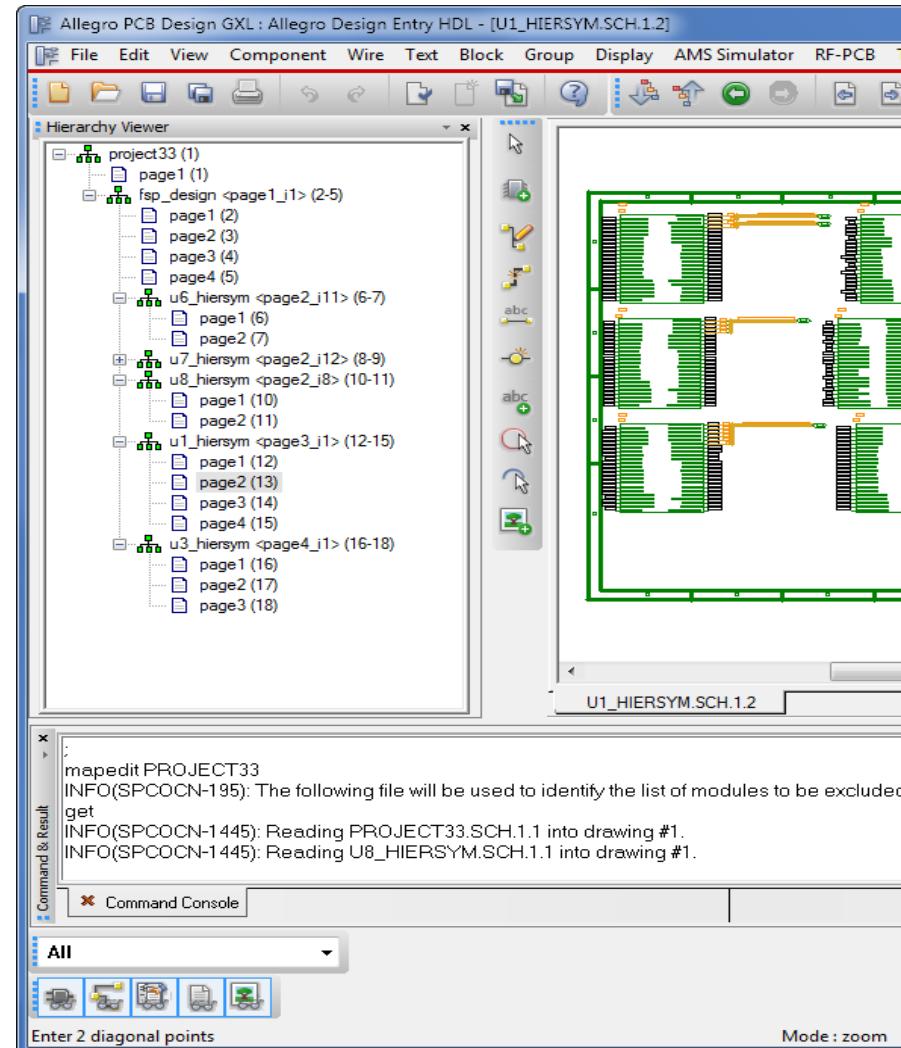

# Генерация схемы и схемных символов

- Схемы автоматически генерируются в FSP

- Либо используйте ваш библиотечный символ, и дайте FSP сгенерировать связи, либо поручите FSP самому сгенерировать и символы ПЛИС, и связи

- Схема для ПЛИС интегрируется в общую схему печатного узла через иерархию

- Эти функции позволяют делать изменения в проекте со значительным снижением затрат

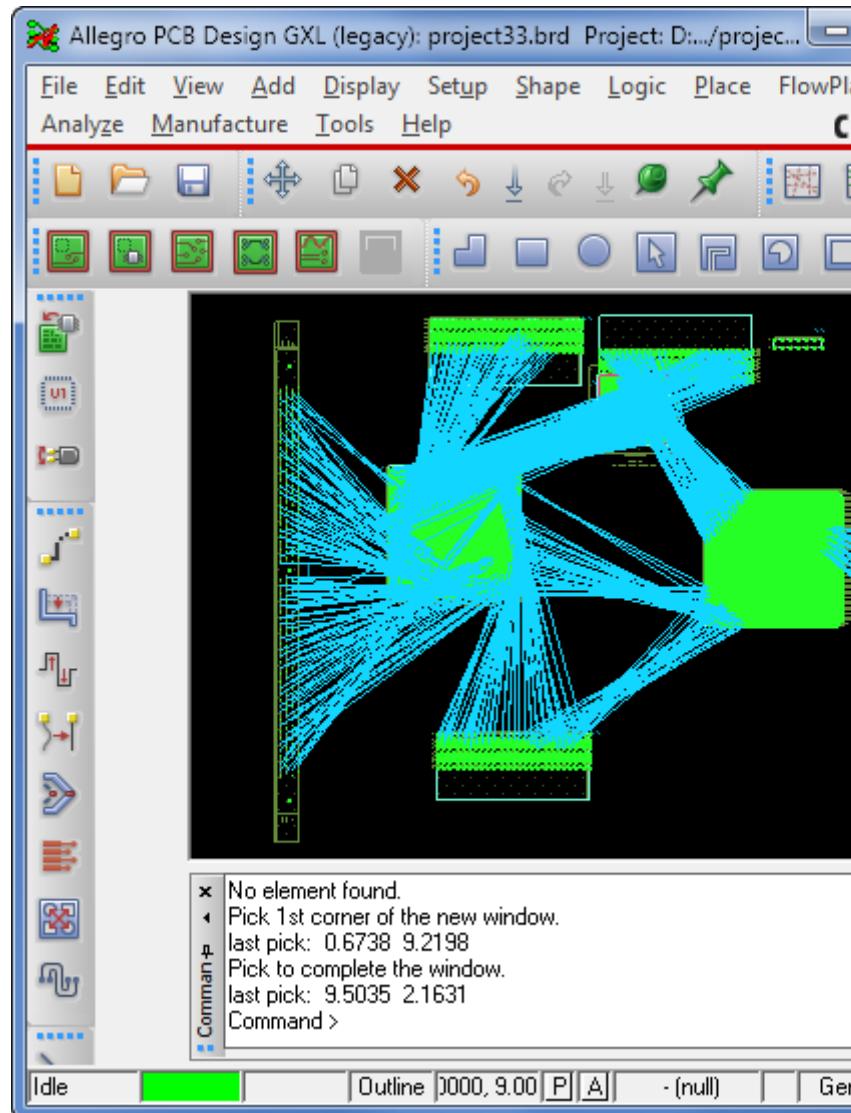

# Оптимизация дизайна в редакторе Allegro PCB (ECO)

- Инженеры-разработчики печатных плат могут выполнять окончательную оптимизацию, используя машинку FSP для управления свопингом

- Изменения полностью совместимы с ПЛИС

- Разработчик может выполнить только корректные изменения

- Это позволяет соединить проекты ПЛИС и печатной платы в единое системно оптимизированное решение

# Выполнение корректировок дизайна

- **Изменения реализуются просто**

- Изменяйте ПЛИС на другую ПЛИС из семейства

- Изменяйте или заменяйте любые компоненты, связанные с ПЛИС

- Переворачивайте ПЛИС на обратную сторону платы, и т.д.

- **Как только изменения сделаны в FSP, они тут же легко распространяются на остальной дизайн**

- Завершение измененного проекта на печатной плате может быть выполнено всего за несколько часов, вместо нескольких дней!

# Маршрут проектирования ПЛИС Cadence FSP

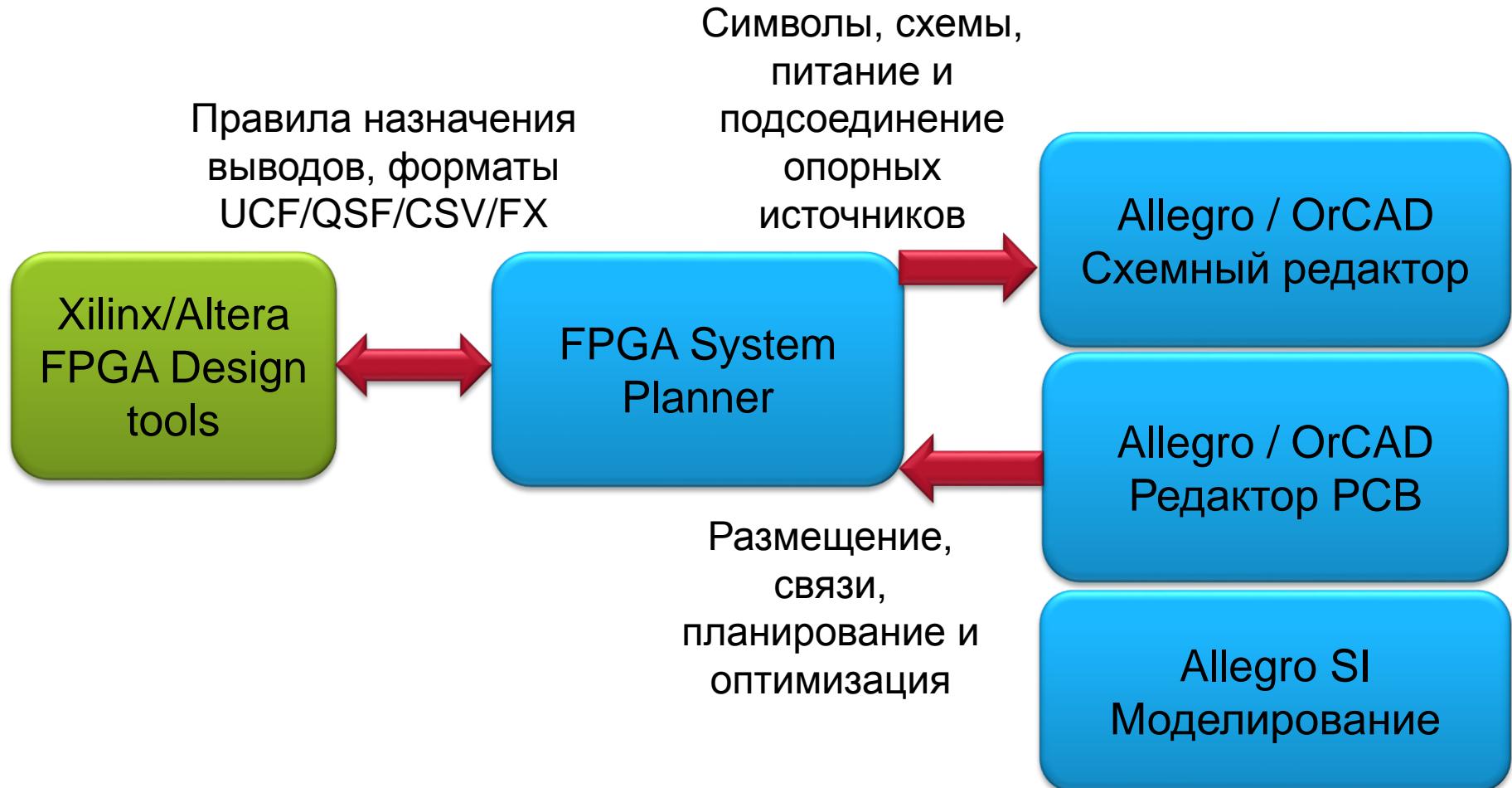

# FPGA System Planner – Интегрированный маршрут

# Маршрут проектирования с Cadence FSP

# Типовые приложения Cadence FSP

# Разработка печатных плат с ПЛИС

- Cadence FSP is integrated with Allegro Design Flow

- FSP can read & use Cadence Schematic libraries

- Integrates seamlessly with existing design processes

- Enables design data reuse across projects

- Using FSP for FPGA board designs enables you to modularize and re-use design data across multiple projects

- Replace your FPGA or other parts in the design easily

- Visualize FPGA design related changes on the pcb within a few hours as opposed to weeks

- Enables quicker revisioning of boards when updating FPGA's and/or obsolete components, etc

# Изучение архитектуры системы с Cadence FPGA System Planner

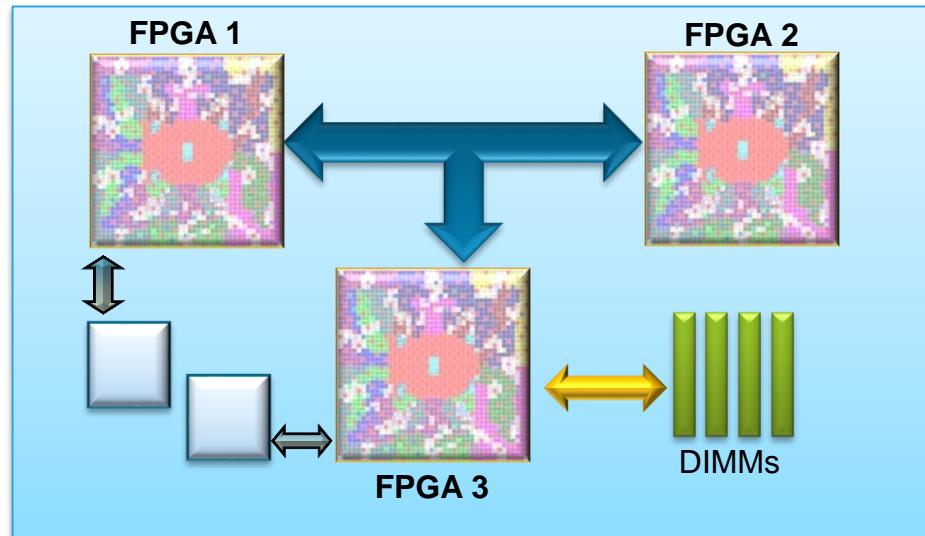

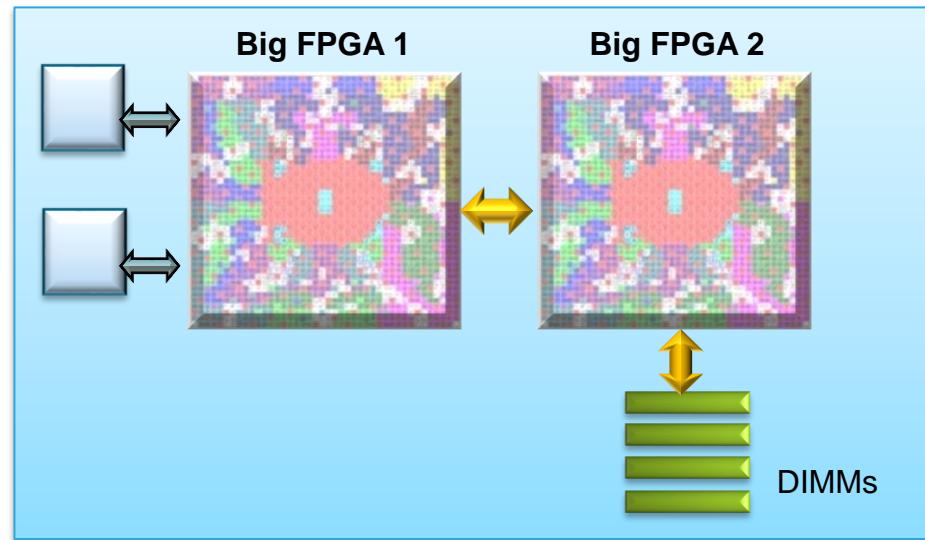

- Cost / Performance trade-offs

- Fewer large FPGAs vs multiple smaller FPGAs

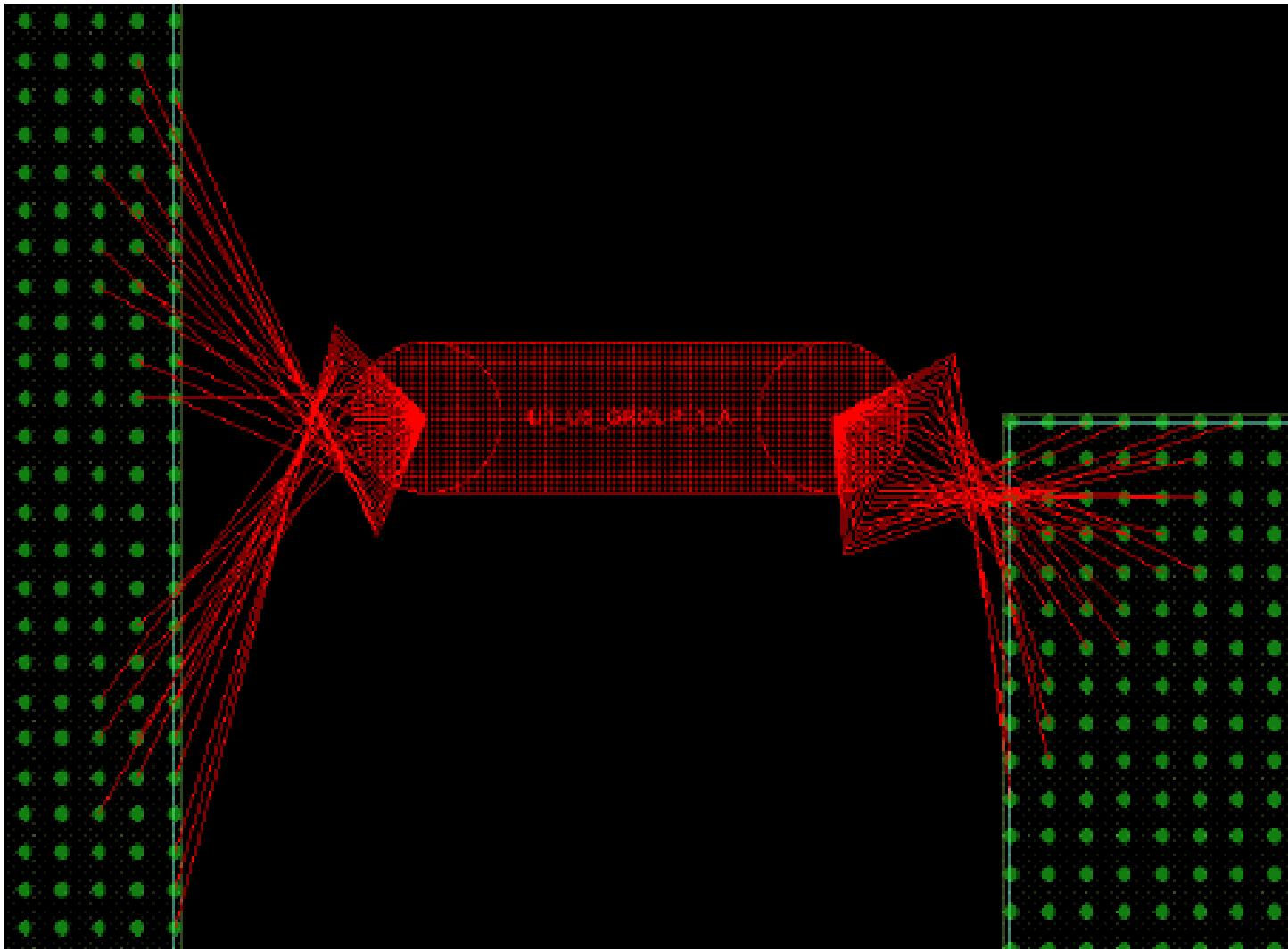

- Automatic I/O pin assignment enables exploration that is not practical with manual approaches

- Board level placement & route exploration

# Прототипирование СБИС

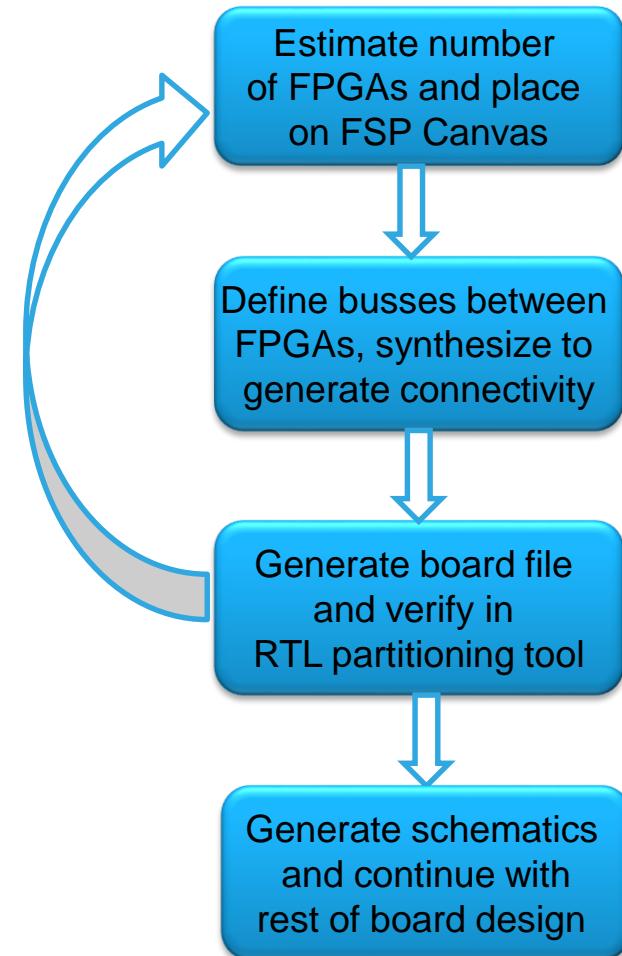

- Enables defining the requirements and designing at an architectural level

- Higher level of abstraction enables easy iterations to ensure requirements are met

- Changes can be propagated incrementally even at late stages of the design

- Board is optimized for both prototype requirements as well as number of layers

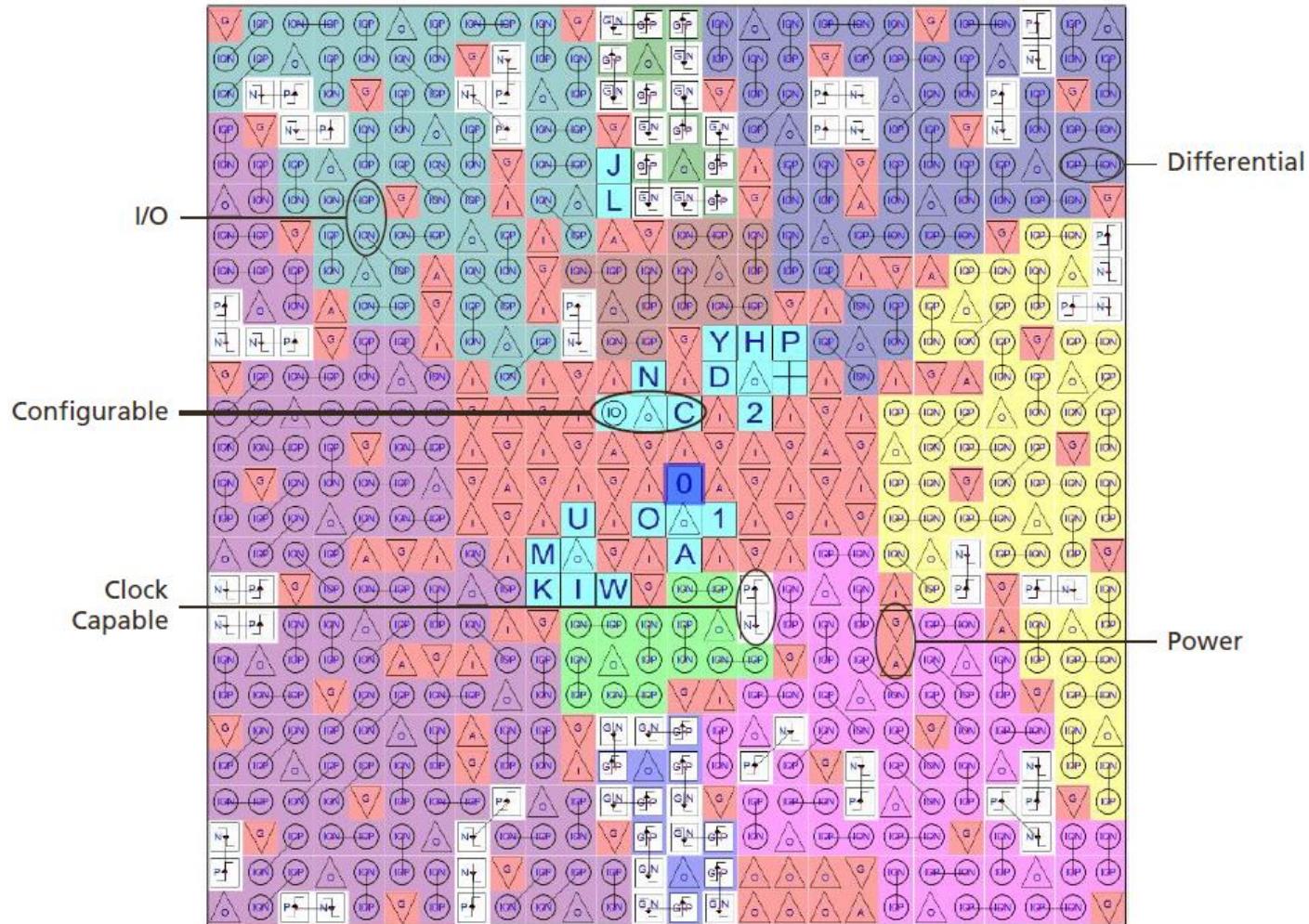

# Пример библиотечного элемента ПЛИС с картой входов/выходов и банков

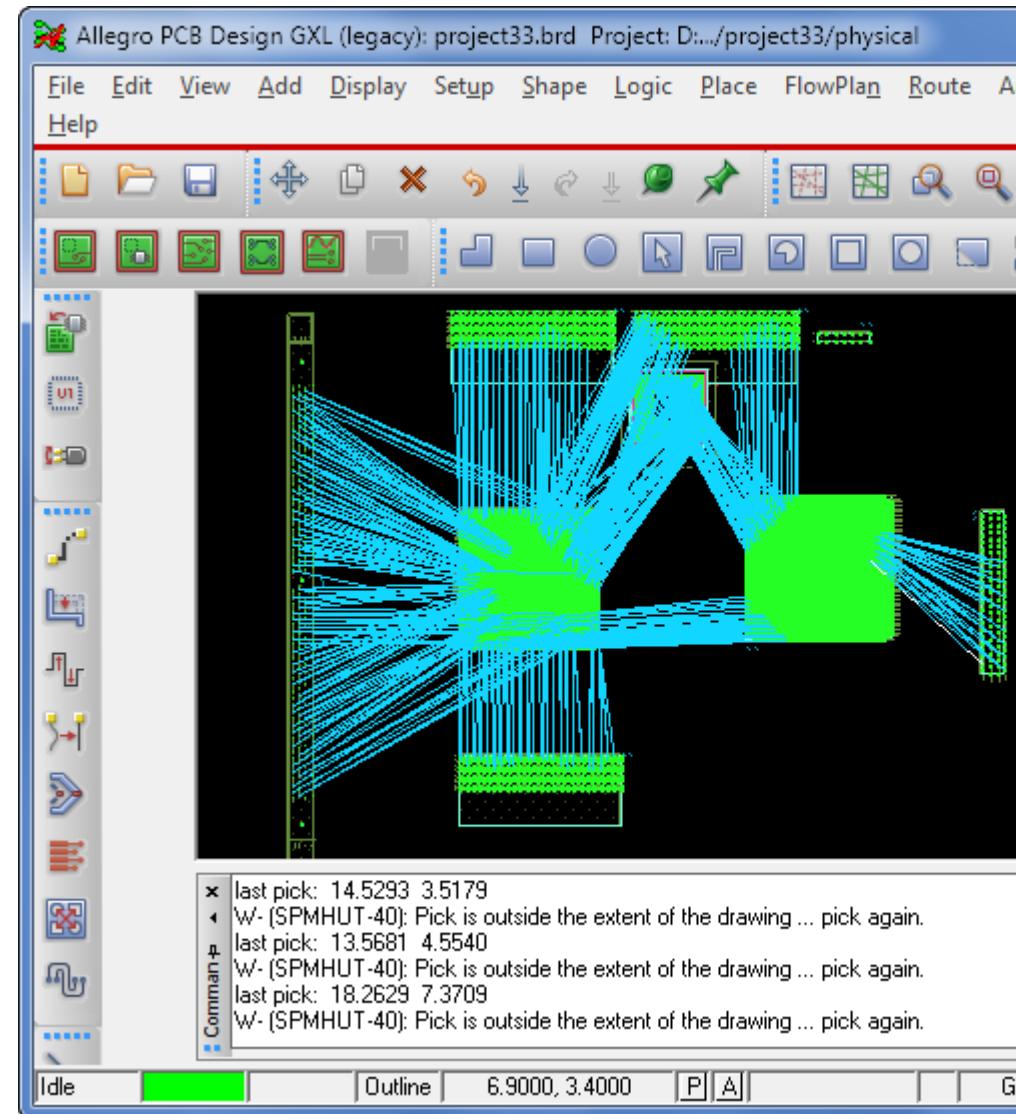

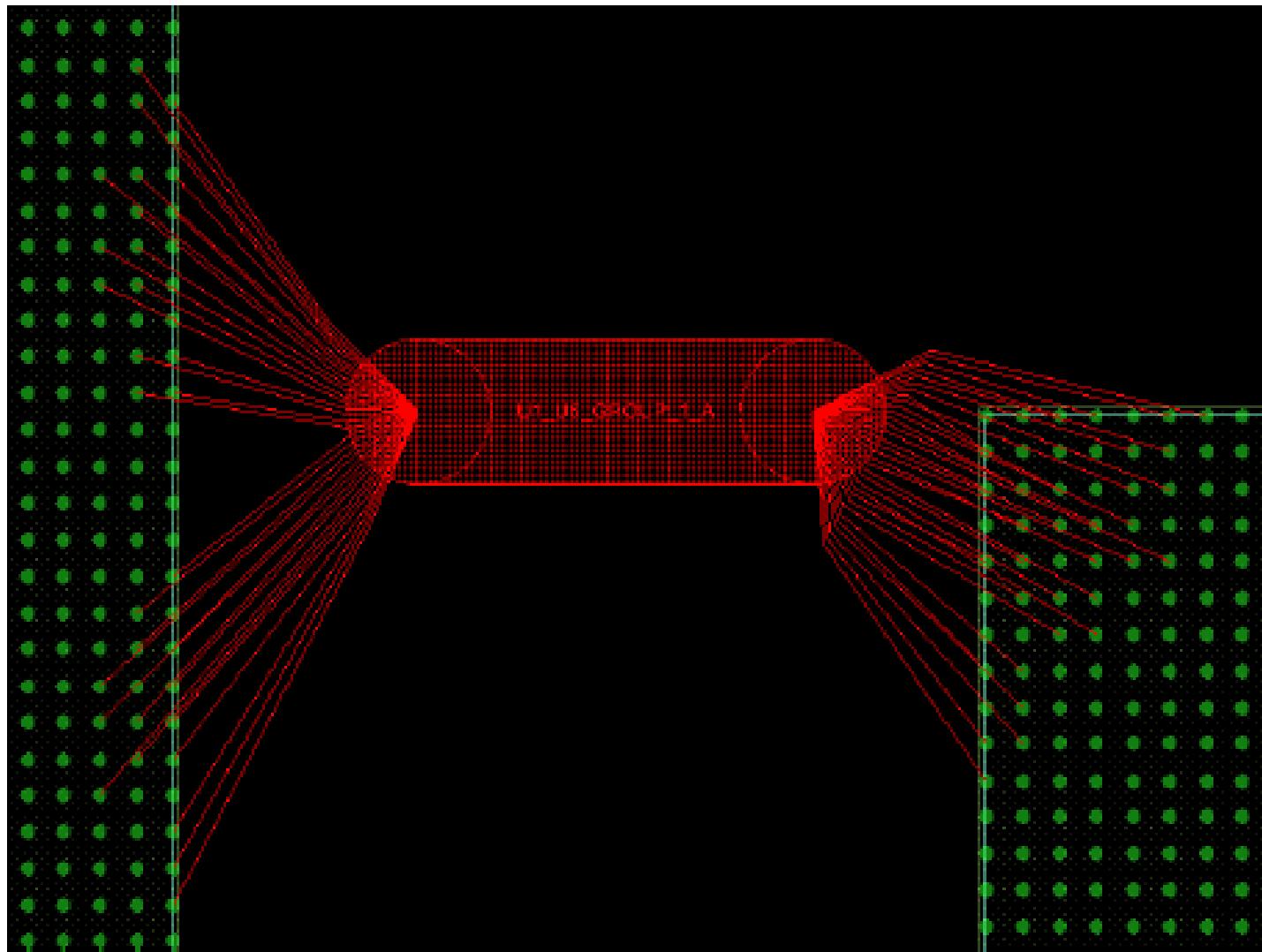

# Визуализация расположения критических элементов для синтеза цоколевки ПЛИС

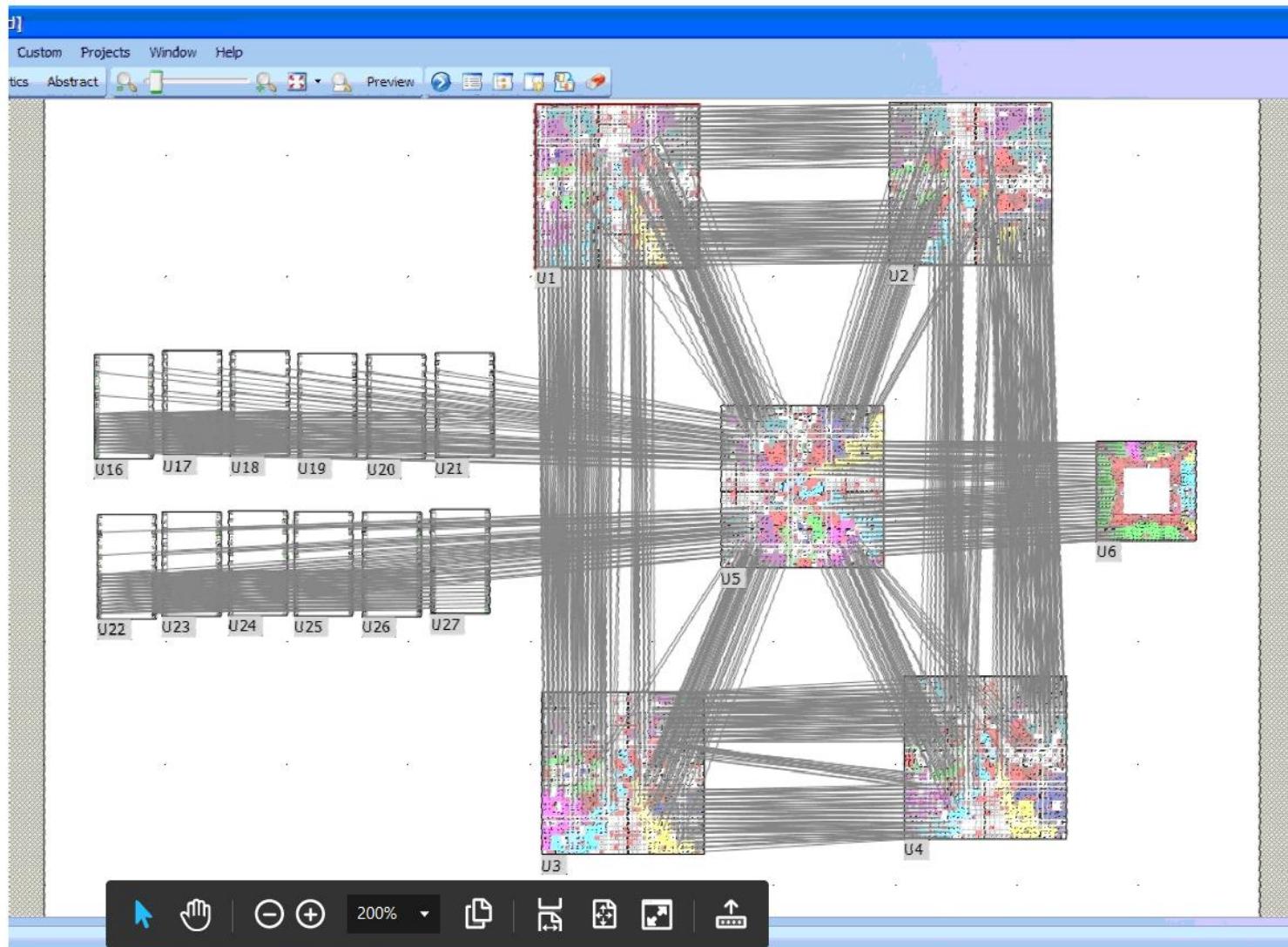

# Конкурентная оптимизация нескольких ПЛИС на основе взаимного расположения

Возможна оптимизация в фоновом режиме

с вызовом из PCB-редактора Cadence Allegro

Возможна оптимизация в фоновом режиме

с вызовом из PCB-редактора Cadence Allegro

cādēnce®